Taiwan Semiconductor Manufacturing Company (TSMC) osiągnęło istny przełom w swoich badaniach nad procesem technologicznym 2 nm. Doniesienia o tym przełomie są szeroko komentowane w tajwańskich mediach. Oczekuje się, że TSMC, która jest głównym wykonawcą procesorów na całym świecie, rozpocznie próbną produkcję tego procesu w połowie 2023 roku. Jednak to rok 2024 będzie najważniejszy, ponieważ to w nim wystartuje produkcja masowa.

Proces technologiczny 2 nm w 2024 roku

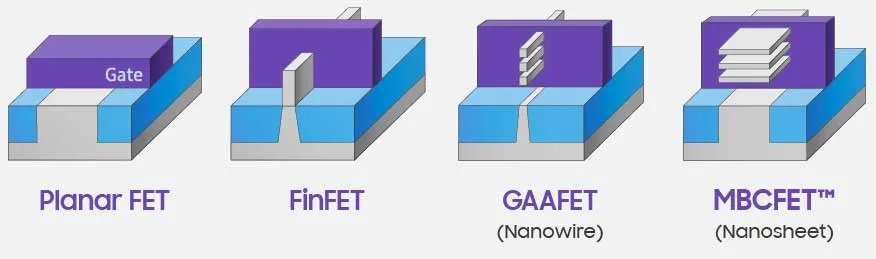

Proces 2 nm TSMC oznaczać będzie duży skok względem aktualnej technologii. Obecnie najniższy proces technologicznty to 5 nm pierwszej generacji. Zostanie on wykorzystany między innymi do budowy procesorów dla smartfonów Apple na rok 2020. Dlaczego to jednak on, a nie proces 3 nm będzie aż tak przełomowy? Otóż w odróżnieniu od 'FinFET’ (Fin Field Effect Transistor), który jest terminem stosowanym do opisu konstrukcji tranzystora w produktach TSMC i Samsunga, proces TSMC 2 nm będzie wykorzystywał konstrukcję tranzystora różnicowego. Konstrukcja ta jest określana jako tranzystor Multi-Bridge Channel Field Effect (MBCFET) i jest uzupełnieniem poprzednich konstrukcji FinFET.

Zobacz też: Holograficzna pamięć masowa – Microsoft ma ambitne plany

Konstrukcja FinFET to po prostu ulepszone tranzystory polowe. Składa się więc z trzech istotnych elementów. Są to: źródło, bramka i dren. Elektrony przemieszczają się od źródła do drenu, a bramka reguluje ten przepływ. W projektach poprzedzających FET źródło i dren były wykonywane tylko w osi poziomej, tzn. leżały płasko z danym chipem. Innowacyjne podejście FinFET podniosło zarówno źródło, jak i spust w trzecim wymiarze, tj. w pionie, co pozwoliło na przepuszczenie większej ilości elektronów przez bramkę, ograniczyło wycieki i zmniejszyło napięcie robocze. Producent poszedł jednak o krok dalej.

Warto tu podkreślić, że technologia MBCFET to pomysł ze stajni Samsunga, który planuje zastosować ją już w procesie 3 nm. Polega on na wykorzystaniu w ramach jednej bramki baterii kilku źródeł i drenów. W ten sposób zwiększa się powierzchnia czynna takiego złącza i umożliwia większy przepływ elektronów przy wykorzystaniu mniejszego napięcia. Opór takiej konstrukcji także będzie znacznie mniejszy. To natomiast oznacza mniejsze zużycie energii i generowanie mniejszych ilości ciepła. Dodatkowo samo zmniejszenie procesu technologicznego zapewni tutaj duży zysk w tej kwestii.

Źródło: wccftech