To świetny czas dla procesorów mobilnych. Firma Apple poczyniła postępy w skokach i granicach na froncie dzięki uprzejmości TSMC w przestrzeni produkcji półprzewodników. Qualcomm i Huawei nie są zbyt daleko w tyle albo, z jedyną firmą wykazującą powolny postęp jest Samsung. Teraz mamy więcej informacji na temat planów TSMC dotyczących węzła wydajności nowej generacji.

Procesory wykonane w procesie 5 nm pojawią się już w 2021 roku

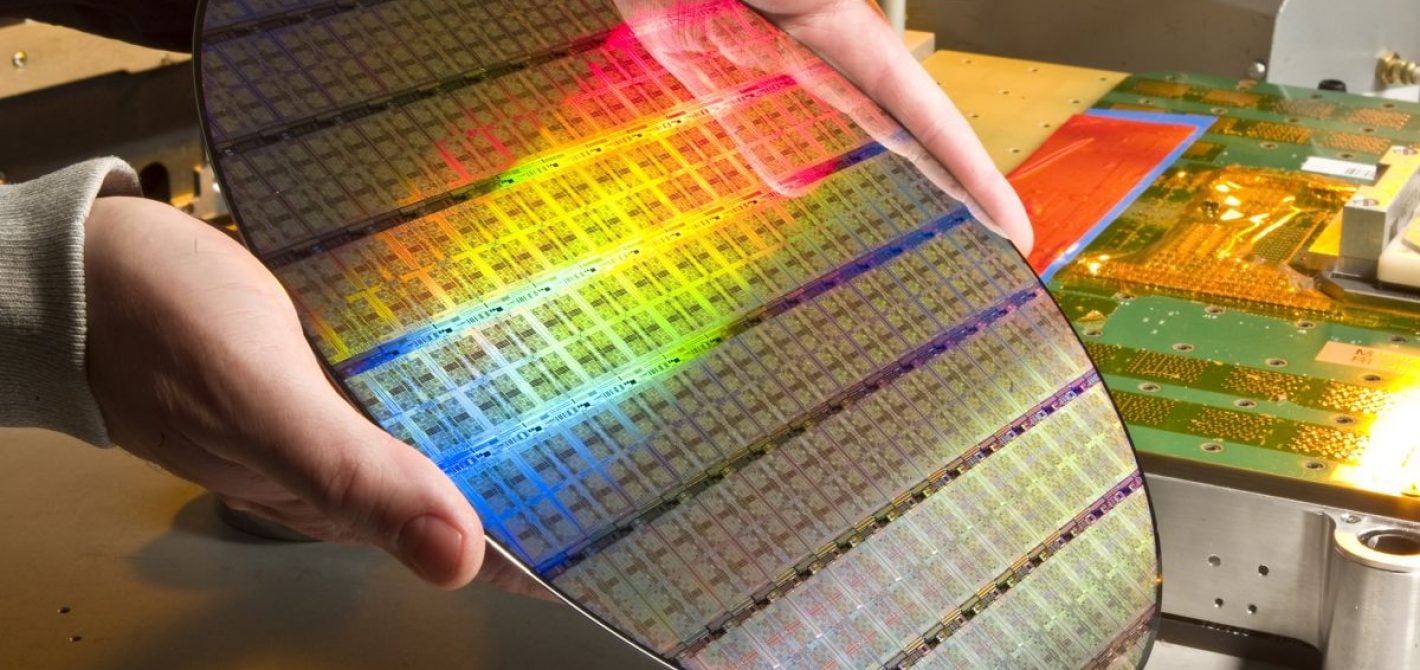

TSMC pomyślnie zakończyło próbną produkcję płytek 5 nm na Fab 18. Firma spodziewa się wejść do masowej produkcji w przyszłym roku, z 5 nm+. W ubiegłym miesiącu poinformowaliśmy, że TSMC rozpoczęło produkcję układów w procesie produkcyjnym następnej generacji 5 nm. Oczekuje się, że węzeł 5 nm zapewni 80% wzrost gęstości tranzystorów, 15% wzrost wydajności i 40% redukcję powierzchni. Proces ten zostanie zastosowany w przypadku kilku produktów z roku 2021. Istnieje duża szansa, że jednym z nich bedzie Apple A14. Według nieoficjalnych informacji próbna produkcja TSMC na poziomie 5 nm została zakończona. Oznacza to, że TSMC powinno być gotowe do rozpoczęcia masowej produkcji, gdy uzna to za stosowne. Jest to ciekawy raport, ponieważ produkcja rdzeni dla tego procesu rozpoczęła się dopiero w zeszłym miesiącu.

Zobacz też: Huawei P Smart Z przedstawiony – wysuwany aparat to niejedyny jego atut

Raport ITHome spodziewa się również, że produkcja TSMC w technologii 5 nm rozpocznie się w drugim kwartale 2020 roku. Dodatkowo zawiera on również szczegóły dotyczące planów TSMC na 5 nm+. Proces ten zwiększy wydajność o 7% przy poziomach zużycia energii zbliżonych do procesu 5 nm. Jak wynika z informacji, produkcja próbna dla 5 nm+ rozpocznie się w pierwszym kwartale przyszłego roku. Natomiast produkcja masowa rozpocznie się w roku 2021. Według danych IBS Researc, cena wafla krzemowego 5 nm wyniesie 12 500 USD. Dla porównania wafel wykonany w procesie 7 nm kosztuje 9 965 USD. Jednak proces ten pozwoli na zastosowanie do 10,5 mld tranzystorów na matrycy o powierzchni 85 mm². Jednak wzrost ten zostanie skompensowany zmniejszoną wartością NDPW (Net Die Per Wafer) wynoszącą 530,25 ze względu na zmniejszoną wydajność procesu.

Źródło: wccftech